Bài học

Nhiễu và chống nhiễu board mạch điện tử

Nhiễu và chống nhiễu board mạch điện tử

Khái niệm về nhiễu board mạch

Nhiễu (noise) trong thiết kế mạch điện tử là các loại tín hiệu tạp chất được sinh ra một cách ngẫu nhiên gây ảnh hưởng xấu tới tín hiệu thông tin . Có hai loại nhiễu board mạch được chú ý là nhiễu bức xạ ( Radiation noise) và nhiễu thu nhận ( reception noise). Nhiễu bức xạ là loại nhiễu do chính thiết bị hoặc mạch điện đó gây ra còn nhiễu thu nhận là loại nhiễu do thiết bị hoặc mạch điện đó nhận được khi hoạt động gần các nguồn nhiễu.

Khái niệm nhiễu thường đi chung với khái niệm EMC(Electromagnetic compatibility) – khả năng tương thích điện từ mà được hiểu là gồm 2 loại: nhận điện từ – EMI(Electromagnetic interference) và miễn nhiễm điện từ -EMS(Electromagnetic Susceptibility). Việc giảm nhiễu là việc phải kết hợp giải quyết 2 vấn đề là giảm EMI và tăng EMS.

Chống nhiễu board mạch để làm gì?

Trong việc thiết kế mạch điện tử, nhất là mạch điện tử tốc độ cao thì việc chống nhiễu là việc cần phải lưu ý và phải làm từ khâu khởi tạo dự án. Chúng ta không thể đợi khi đã thiết kế mạch xong rồi mới bắt đầu kiểm tra nhiễu vì muốn cải tạo bất cứ gì thì sẽ phải thay đổi lại toàn bộ thiết kế làm tốn thời gian thiết kế, làm mạch và chi phí đặt mạch.

Nhiễu không thể mô phỏng trước được vì nó mang tính ngẫu nhiên do thiết kế. Việc tính toán khử nhiễu là tương đối khó khăn đối với người không có kinh nghiệm nên đòi hỏi người làm mạch phải có những kiến thức nhất định trong thiết kế mạch. Một điều đáng lưu tâm nữa là khi kết hợp quá nhiều phương pháp khử nhiễu trên một mạch điện PCB có thể khiến bạn mất một chi phí khá lớn vượt qua chi phí dự trù ban đầu để tạo ra thiết bị đó. Do vậy việc cần làm là khử nhiễu một cách có hiệu quả vừa đủ để thiết bị hoạt động ổn định và tiết kiệm chi phí.

Nhiễu board mạch do đâu

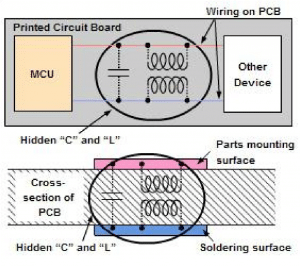

Các cuộn cảm ẩn và tụ điện ẩn là các cảm kháng ảo tồn tại trong mạch điện PCB ( printed circuit board) là một trong các nguyên nhân gây nhiễu. Các thành phần cảm kháng này tồn tại giữa hai đường mạch hoặc là giữa hai lớp chất liệu đối với mạch nhiều lớp.

Do quá trình thiết kế PCB, người thiết kế đã tiến hành đi hai hay nhiều dây tín hiệu song song quá gần với nhau hoặc do đặc trưng của board mạch in PCB mà có thể tạo ra các giá trị khác nhau của tụ điện ẩn và cuộn cảm ẩn, những thành phần này góp phần vào gây ảnh hưởng qua lại tín hiệu từ đường mạch in này lên đường mạch in khác:

Chống nhiễu board mạch như thế nào

Bởi vậy, tại bước đầu tiên của làm mạch in PCB, người thiết kế phải chú tâm tới khoảng cách giữa các dây tín hiệu và độ dày, chất liệu của board mạch in. Đối với các công ty làm mạch in PCB, có một khuyến cáo là thiết bị CNC của họ có thể đi được các đường dây có khoảng cách tối thiểu là bao nhiêu, với độ dày là bao nhiêu. Người làm mạch cần nghiên cứu kĩ điều này trước khi đặt mạch tại các công ty làm mạch để tránh phải vẽ lại thiết kế do nhà làm mạch không thể đáp ứng được yêu cầu, mỗi lần vẽ lại sẽ rất mất thời gian. Ví dụ: công ty KimSonpcb là một công ty làm mạch lớn tại HCM có quy cách mạch in khuyến cáo là đường mạch tối thiểu 8mil, khoảng cách hai đường mạch tối thiểu 8mil.

Tuy nhiên chúng ta nên đi dây khoảng cách và kích thước lớn hơn 10mil để hạn chế lỗi mạch, như thế sẽ tốt hơn.

Kích thước đường mạch càng nhỏ thì càng ít nhiễu nhưng phải đảm bảo đường mạch chịu được dòng điện theo thiết kế, khoảng cách giữa các đường mạch càng rộng càng tốt.

Công cụ trên trang: https://www.eeweb.com/tools/microstrip-impedance cho phép ta tính toán các chỉ số cần thiết khi thiết kế mạch như: tính hệ số nhiễu giữa hai đường mạch có bề rộng W hoặc tính bề rộng tối thiểu đường mạch để chịu được dòng A (Ampere).

Lỗ xuyên via cũng là một trong các nguyên nhân gây nhiễu và lỗi trong mạch PCB. Trong thiết kế chúng ta nên hạn chế tạo lỗ via ít nhất có thể. Điều này là phụ thuộc vào trình độ của người thiết kế.

Các phương pháp khử nhiễu board mạch

Các loại nhiễu thường gặp

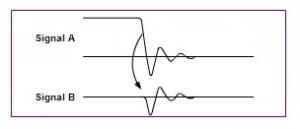

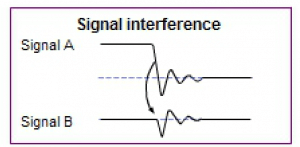

Nhiễu do ảnh hưởng qua lại của tín hiệu bị gây ra do sự thay đổi đột ngột mức điện áp của tín hiệu A làm tín hiệu B cũng bị ảnh hưởng theo. Loại nhiễu này phát sinh do các thành phần cảm kháng ẩn như đã trình bày ở trên.

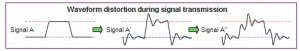

Một tín hiệu A được tạo thành bởi một linh kiện, nhưng trên đường truyền, trở kháng ở đầu ra của linh kiện đó và đầu vào của linh kiện khác có sự khác nhau sẽ gây ra hiện tượng phản xạ sóng tại linh kiện nhận. Sóng phản xạ sẽ gây chồng lấp lên tín hiệu chính và gây biến dạng tín hiệu. Đây cũng chính là nguyên nhân chúng ta phải phối hợp trở kháng để đảm bảo tín hiệu thông tin được toàn vẹn nhất.

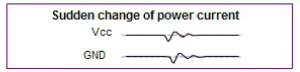

Nguồn điện cung cấp cho mạch điện đôi khi không ổn định cũng gây ảnh hưởng xấu tới mạch điện. Lúc này các tụ lọc là thực sự cần thiết để ổn định nguồn. Đối với tín hiệu tần số cao, tụ điện đóng vai trò như một điện trở và giá trị điện trở đó phụ thuộc và điện dung tụ và tần số tín hiệu. Công thức được mô tả:

Ví dụ đối với tín hiệu có tần số100Mhz, tụ có điện dung 10pF có trở kháng là Zc=170(Ohm)

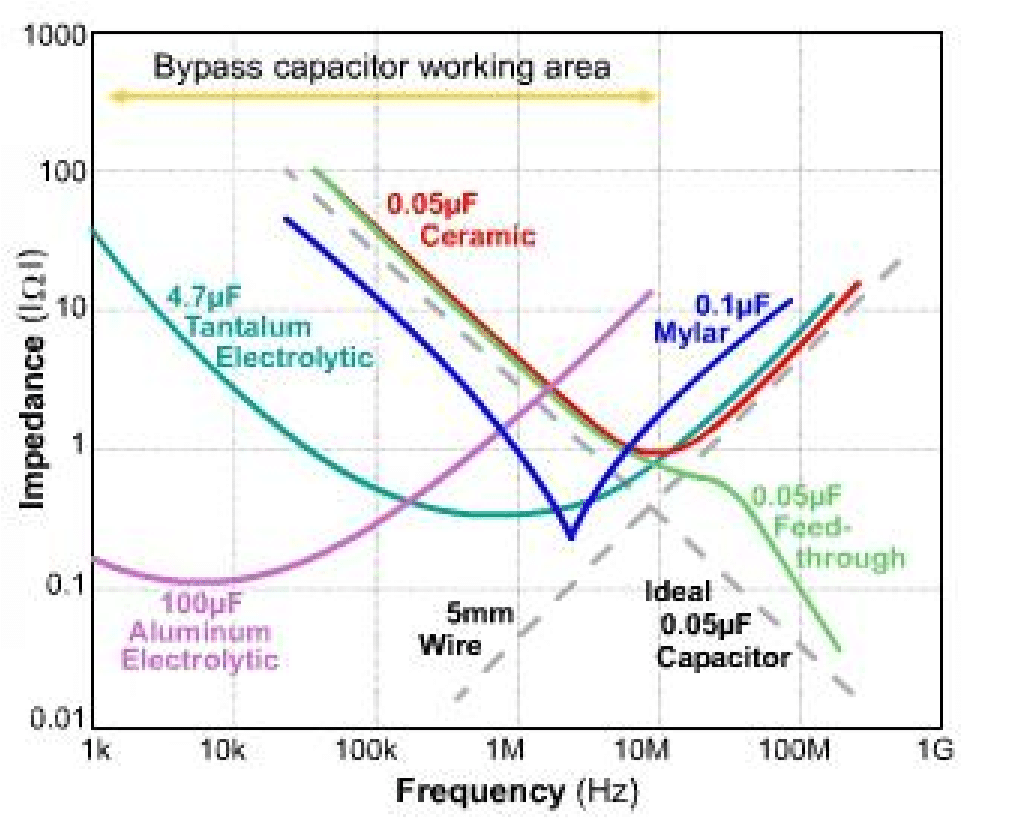

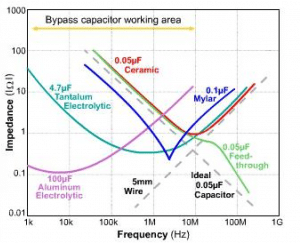

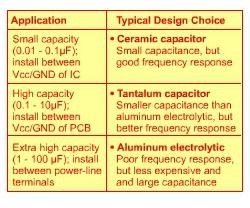

Bảng sau cho ta biết mức độ đáp ứng trở kháng của các giá trị tụ khác nhau đối với các tần số khác nhau của hệ thống.

Từ đó chúng ta có thể chọn các loại tụ khác nhau để lọc nhiễu cho các ứng dụng khác nhau,đối với nguồn cấp gần IC hoặc các ngoại vi thì dùng tụ cỡ 0.01-0.1uF nối giữa VCC và GND cho ta kết quả tốt nhất. Vì nó sẽ làm giảm trở kháng đường dây nguồn IC ở khoảng tần số cỡ MHZ. Còn đối với nguồn chính thì nên dùng tụ lọc có giá trị lớn hơn khoảng tầm 1-100uF để khử các thành phần răng cưa thường thấy ở đường nguồn. Nhưng không nên dùng tụ có giá trị quá lớn vì dòng khởi động có thể gây nguy hại cho mạch PCB khi cấp nguồn.

Các phương pháp khắc phục nhiễu

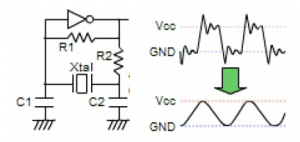

Điều chỉnh giá trị của tụ và trở lọc nhiễu cho bộ tạo dao động thạch

Trước tiên là nếu như có thể thì hãy chọn thạch anh có tần số nhỏ nhất mà đáp ứng được yêu cầu thiết kế bởi vì tần số càng cao thì chỉ số EMI càng lớn, nhiễu càng dễ xảy ra. Sau đó chúng ta có thể tham khảo sơ đồ khử nhiễu như trên, điều chỉnh các giá trị tụ C1,

C2 và R2 để có kết quả tín hiệu tốt nhất. Thông thường thạch anh có giá trị tầm Mhz thì tụ có giá trị tầm pF.Một điều nữa là thạch anh nên đặt càng gần IC càng tốt.

- Chọn IC dán QFP thay vì IC nổi DIP

Có một điều được khuyến cáo là IC dán cho kết quả chống nhiễu board mạch tốt hơn là IC DIP vì vậy nếu có IC tương đương dạng QFP, hãy sử dụng chúng

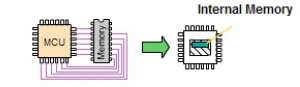

- Chọn IC tích hợp single-chip thay vì chọn một IC và một ngoại vi mở rộng khác

Nguyên nhân của việc chọn này rất đơn giản, vì các dây tín hiệu nối giữa hai linh kiện là một thành phần gây nhiễu không hề nhỏ khi thi công. Nên nếu có thể thì hãy chọn loại IC đã tích hợp

(single-chip)

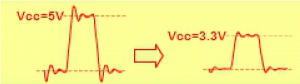

- Chọn nguồn cung cấp có giá trị nhỏ nếu IC có thể chạy được

Đây là một cách tương đối đơn giản, bởi vì công suất nhiễn tỉ lệ với bình phương biên độ điện áp :P=VI=V2Z. Bởi vậy thay vì dùng nguồn 5V và dùng nguồn 3.3V thì sẽ giảm một lượng nhiễu đáng kể( thông thường việc làm giảm được 57% nhiễu)

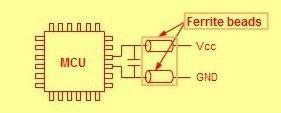

- Lọc nhiễu bằng bộ lọc LC

Đây là một cách phổ biến được dùng hiện nay, cuộn Ferrite bead có chức năng chặn cao tần và tụ thì có chức năng làm mượt tín hiệu. Tuy nhiên cần chú ý là không đặt ferrite bead tại đường tín hiệu có tần số cao hoặc là đường clock vì cuộn ferrite có thể gây mất tín hiệu trên đường truyền. Thông thường người ta đặt ferrite bead tại đường nguồn của thiết bị. Việc này cũng góp phần làm cho IC và các linh kiện trong mạch bớt nóng hơn.

- Hạn chế nhiễu bằng chính quy trình thiết kế PCB

Cách này phụ thuộc vào trình độ của người thiết kế, có một vài lưu ý theo quan điểm người viết:

-Đi dây có ít lỗ xuyên Via nhất

-Đi dây lớn hơn với đường nguồn và nhỏ hơn với đường tín hiệu, ví dụ đối với nguồn 5V thì đường nguồn 40mil và đường tín hiệu 10mil là ổn.

-Hạn chế đường tín hiệu bẻ góc 90 độ, nếu có thì hãy làm mượt nó

-Giữa tụ bypass nguồn của IC không nên đi xuyên via mà hãy đi via ở sau tụ

-Không được đi dây dưới thạch anh dao động

-Sau khi thiết kế, phủ mass GND toàn mạch là việc làm cần thiết

Bạn cũng có thể tham gia khóa học ” Phân tích, thiết kế mạch in dùng Altium Desginer ” tại AHTLAB để được hướng dẫn vẽ mạch in tối ưu nhất